Lichee Tang Nano 20K FPGA使用教程

【简介】

Tang Nano 20K 是采用高云半导体 GW2AR-18 QN88 的一款核心板,芯片内部具有 20736 个逻辑查找表(LUT4) 和 15552 个寄存器(FF),内部有两个 PLL,还带有多个 DSP 单元支持 18位 x 18位 的乘法运算来加速数字运算。板载 BL616 芯片来作为 FPGA JTAG 下载器和与 FPGA 通信的串口。板上默认使用 27MHz 晶振用于倍频出 HDMI 显示所需要的时钟,还额外搭载 MS5351 时钟发生芯片来随意生成多种所需要的时钟。

淘宝购买链接:点我

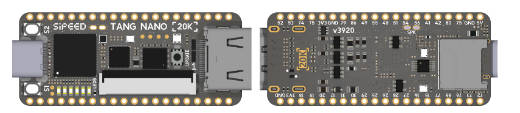

【外观渲染图】

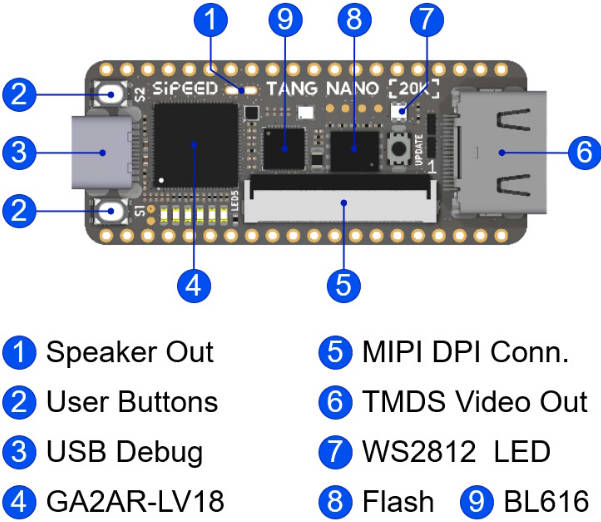

【详细参数】

| 项目 | 参数 | 补充 | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| FPGA 芯片 | GW2AR-LV18QN88C8/I7 |

| ||||||||||||||||||

| 板载下载器 | BL616 | · 给 FPGA 提供 JTAG 下载功能 · 提供 USB 转串口与 FPGA 通信 · 提供虚拟串口用于 FPGA 通过 SPI 通信 · 提供虚拟串口控制 MS5351 输出时钟 | ||||||||||||||||||

| 时钟芯片 | MS5351 | 给 FPGA 芯片提供额外的三路时钟 点我查看 MS5351 配置方法 | ||||||||||||||||||

| 显示接口 | · 40Pins RGB lcd 连接器 · HDMI 接口 | |||||||||||||||||||

| 单色 LED | 6 个 | 共阳极连接 | ||||||||||||||||||

| RGB LED | 1 个 | 型号是 WS2812 | ||||||||||||||||||

| 用户按键 | 2 个 | 用于自定义逻辑功能 | ||||||||||||||||||

| TF 卡槽 | 1 个 | 推拉式 | ||||||||||||||||||

| 功率放大器 | 1 个 | 型号是 MAX98357A,用于播放音频 | ||||||||||||||||||

| 存储 | 64Mbits Flash | 下载方式参考底部相关问题 | ||||||||||||||||||

| 尺寸 | 22.55mm x 54.04mm | 精确尺寸可以参考 3D 文件 |

【外设框图】

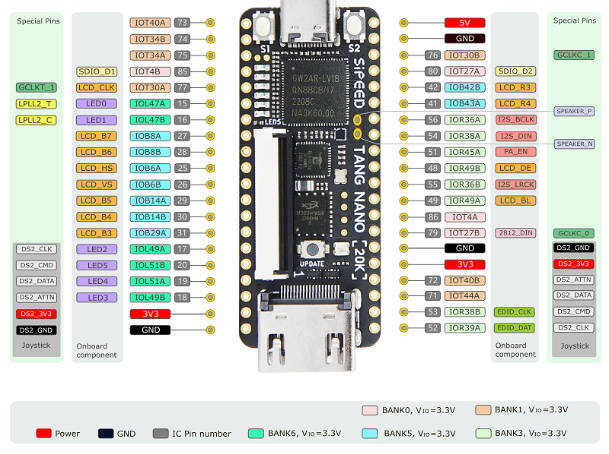

【引脚框图】

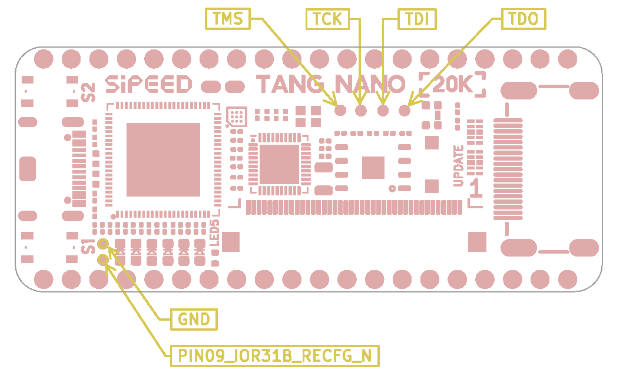

【FPGA Jtag 触点指示图】

我们在 Tang Nano 20K 上引出了 Jtag 触点,方便想要使用额外下载器的用户。

Tang Nano 20K 板卡上是带有下载器的,这个测试点只是给有额外需要的人准备的。

【硬件资料】

板卡规格书

板卡原理图

PCB BOM (根据自己板子的版本查看里面的 html 文件)

板卡尺寸图

板卡 3D 模型

部分芯片手册

【上手使用】

安装 IDE -> 编写代码 -> 烧录进板子

更多例程代码 github

】其他学习资源

- 在线免费教程:Verilog 教程(学习Verilog)

- 在线免费 FPGA 教程:Verilog (英文网站)

- Verilog 刷题网站:HDLBits(英文网站)

- 在线高云半导体可参考视频教程:点击这里

【常见问题】

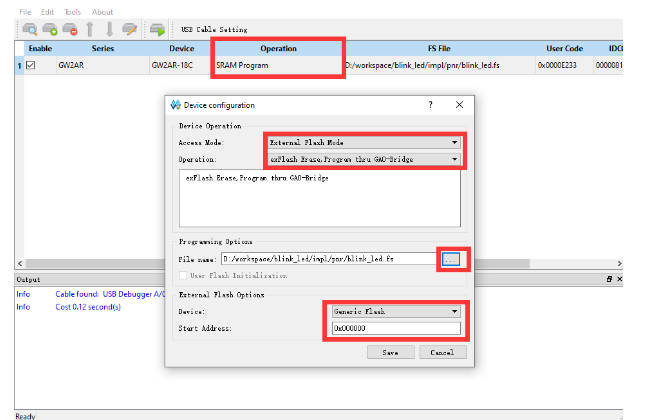

】怎么让固件上电启动

Tang Nano 20K 使用外部 Flash 来存放固件,所以想要让固件存在板子上我们需要烧录到外部 Flash.

】更多问题前往 Tang 常见问题 查看

【售后】

周一-周五(9:30-6:30)周六(9:30-5:30)

手机:13434470212

邮箱:services04@spotpear.cn

QQ:202004841